Transistor Evolution- Planar မှ CFET အထိ၊ 3D ပေါင်းစပ်မှုသည် Semiconductor တိုးတက်မှုကို ပြန်လည်သတ်မှတ်သည်

ရာစုနှစ်တစ်ဝက်ကျော်ကြာတွင်၊ တစ်ပိုင်းလျှပ်ကူးစက်လုပ်ငန်းသည် ရိုးရှင်းသောစည်းမျဉ်းတစ်ခုအတိုင်း ကြီးထွားလာခဲ့သည်- ထရန်စစ္စတာများကို သေးငယ်အောင်လုပ်ပါ။ကျုံ့သွားသော အင်္ဂါရပ်အရွယ်အစားများသည် စွမ်းဆောင်ရည်ပိုမြင့်ပြီး၊ ပါဝါနည်းပြီး ထရန်စစ္စတာတစ်ခုလျှင် ကုန်ကျစရိတ်သက်သာသည်။သို့သော် ယနေ့တွင် ဤလမ်းသည် ၎င်း၏ရုပ်ပိုင်းဆိုင်ရာနှင့် စီးပွားရေး ကန့်သတ်ချက်သို့ ရောက်ရှိသွားပြီဖြစ်သည်။စင်စစ် ချဲ့ထွင်သည့်ခေတ်သည် ကုန်ဆုံးသွားပြီး ခေတ်သစ်ဖြစ်သည်။ ဖွဲ့စည်းပုံ ဆန်းသစ်တီထွင်မှုနှင့် 3D ပေါင်းစပ်မှု စတင်ပါပြီ။

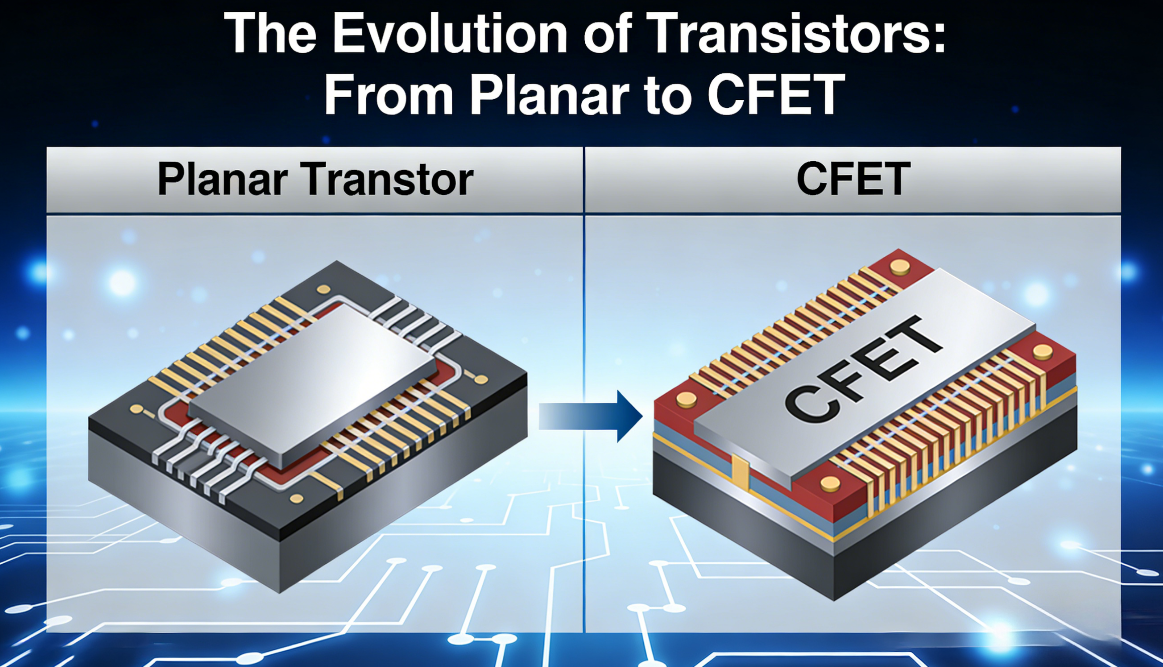

ထရန်စစ္စတာကိုယ်တိုင်က ပြီးပြည့်စုံသော ဗိသုကာတော်လှန်ရေးကို ကြုံတွေ့နေရသည်။Planar MOSFET မှ FinFET အထိ၊ GAA nanosheet မှ CFET stacking အထိ၊ အဆင့်တစ်ခုစီသည် ကျုံ့ခြင်းမှ ရွေ့ခြင်းကို ကိုယ်စားပြုသည် Transistor ကို သုံးဖက်မြင်ဖြင့် ပြန်လည်တည်ဆောက်သည်။.၎င်းသည် တိုးမြင့်လာရုံသာမကဘဲ၊ ၎င်းသည် ချစ်ပ်များ၏ စွမ်းဆောင်ရည်ကို မည်ကဲ့သို့ ဖြည့်ဆည်းပေးသည်ကို ပြီးပြည့်စုံသော ပြန်ဆိုချက်တစ်ခုဖြစ်သည်။

Transistor ဗိသုကာ မျိုးဆက် လေးဆက်

1. Planar Transistor (ရိုးရာ 2D)

တံခါးသည် အထက်မှချန်နယ်ကို ထိန်းချုပ်သည့် ဂန္တဝင်အပြားပုံစံဖြစ်သည်။၎င်းသည် အစောပိုင်းကာလများမှ 40nm နှင့် 28nm အထိ လွှမ်းမိုးထားသည်။အတိုင်းအတာများ ပိုမိုကျုံ့လာသည်နှင့်အမျှ ယိုစိမ့်သောလျှပ်စီးကြောင်းနှင့် လျှပ်စစ်ဓာတ်ထိန်းစနစ်သည် ဖြေရှင်း၍မရသော ပြဿနာများ ဖြစ်လာခဲ့သည်။

2. FinFET (3D ဂိတ်ထိန်းချုပ်မှု)

ချန်နယ်သည် ဒေါင်လိုက် “ဆူးတောင်” ဖြစ်လာပြီး တံခါးသည် နှစ်ဖက်စလုံးကို ရစ်ပတ်ထားသည်။၎င်းသည် အီလက်ထရွန်းနစ်ထိန်းချုပ်မှုကို သိသိသာသာ တိုးတက်ကောင်းမွန်စေပြီး ယိုစိမ့်မှုကို လျှော့ချပေးပြီး 7nm၊ 5nm နှင့် 3nm တို့ကိုပင် ချဲ့နိုင်သည်။FinFET သည် ခေတ်မီစွမ်းဆောင်ရည်မြင့် ချစ်ပ်ခေတ်၏ အခြေခံအုတ်မြစ်ဖြစ်လာခဲ့သည်။

3. GAA နာနိုစာရွက် (ဂိတ်-ပတ်ပတ်လည်)

2nm နှင့် အောက် တွင် FinFET သည် ၎င်း၏ ကန့်သတ်ချက်ကို ထိသွားပါသည်။GAA သည် အလျားလိုက် nanowires သို့မဟုတ် အခင်းအကျင်းများဖြင့် ဆူးတောင်ကို တံခါးဖြင့် အပြည့်ပတ်ထားသည်။၎င်းသည် ပိုမိုကောင်းမွန်သော ထိန်းချုပ်မှု၊ ပါဝါနိမ့်မှုနှင့် ပိုမိုမြင့်မားသော drive current ကို ပေးဆောင်သည်။GAA သည် TSMC၊ Samsung နှင့် Intel တို့ရှိ 2nm အတန်းအစား ချစ်ပ်များအတွက် ပင်မဖွဲ့စည်းပုံဖြစ်သည်။

4. CFET (ဖြည့်စွက် FET)

နောက်နယ်နိမိတ်- NMOS နှင့် PMOS တို့ကို ဒေါင်လိုက်တန်းစီထားသည်။CFET သည် ထရန်စစ္စတာနှစ်လုံးကို တစ်ခု၏ခြေရာသို့ ထုပ်ပိုးထားပြီး ဧရိယာကို သိသိသာသာ လျှော့ချပေးပြီး သိပ်သည်းဆကို မြှင့်တင်ပေးသည်။၎င်းသည် စစ်မှန်သော 3D စနစ်ပေါင်းစည်းမှု မပြီးဆုံးမီ ထရန်စစ္စတာစကေးချဲ့ခြင်း၏ အဆုံးစွန်သော ဆင့်ကဲဖြစ်စဉ်ဖြစ်သည်။

Scaling တစ်ယောက်တည်း ဘာကြောင့် အလုပ်မဖြစ်တော့ဘူး။

- node အသစ်တစ်ခုစီတွင် လုပ်ငန်းစဉ်ကုန်ကျစရိတ်သည် အဆတိုးမြင့်လာသည်။

- ကွမ်တမ်ယိုစိမ့်မှုနှင့် ရုပ်ပိုင်းဆိုင်ရာကန့်သတ်ချက်များသည် ကန့်သတ်ချက်များကို ခိုင်မာစေသည်။

- အပြန်အလှန်ချိတ်ဆက်မှုနှောင့်နှေးမှုနှင့် ပါဝါသုံးစွဲမှုသည် ထရန်စစ္စတာအမြန်နှုန်းကို ကျော်တက်သည်။

- ကြီးမားသော monolithic ချစ်ပ်များသည် အထွက်နှုန်းနည်းပြီး ကုန်ကျစရိတ်မြင့်မားခြင်းမှ ကြုံတွေ့ရသည်။

လုပ်ငန်းက သဘောပေါက်ပါပြီ- စွမ်းဆောင်ရည် သေးငယ်သော ထရန်စစ္စတာများမှ လာမည်မဟုတ်တော့ပါ။ဆီက လာတာ ပိုမိုကောင်းမွန်သောချိတ်ဆက်မှုများ၊ ပိုမိုစမတ်ကျသောဗိသုကာပညာနှင့် ဒေါင်လိုက်ပေါင်းစပ်မှု.

ခေတ်သစ်- 3D ဆန်းသစ်တီထွင်မှု အလွှာသုံးခု

တစ်ပိုင်းလျှပ်ကူးပစ္စည်း တိုးတက်မှုကို 3D ဒီဇိုင်း၏ အတိုင်းအတာသုံးမျိုးဖြင့် သတ်မှတ်သည်-

- 3D TransistorFinFET၊ GAA၊ CFET – ထရန်စစ္စတာကို ဒေါင်လိုက်တည်ဆောက်ခြင်း။

- 3D စက်ပစ္စည်းကို တွဲတင်ခြင်း။: ယုတ္တိဗေဒ၊ ပေါင်းစပ်ချိတ်ဆက်မှု၊ SRAM ပေါင်းစည်းခြင်းဆိုင်ရာ မှတ်ဉာဏ်

- 3D စနစ်ပေါင်းစည်းခြင်း။: Chiplet၊ 2.5D/3D ထုပ်ပိုးမှု၊ အပြန်အလှန်ချိတ်ဆက်မှု-အခြေခံ ပေါင်းစပ်မှု

အတူတူ ဖွဲ့ကြတယ်။ 3D×3D×3D ခေတ်- ထရန်စစ္စတာ၊ စက်ပစ္စည်းနှင့် စနစ်အားလုံးသည် သုံးဖက်မြင်ဖြစ်လာသည်။

DTCO- ပင်မစွမ်းရည်အသစ်

အတိုင်းအတာ အဆုံးသတ်သည်နှင့်အမျှ၊ ဒီဇိုင်းနည်းပညာ ပူးပေါင်းလုပ်ဆောင်ခြင်း (DTCO) ဝေဖန်ပိုင်းခြားမှု ဖြစ်လာသည်။၎င်းသည် ပူးတွဲဒီဇိုင်းထုတ်သည့် ဗိသုကာပညာ၊ ထရန်စစ္စတာဖွဲ့စည်းပုံ၊ သတ္တုလမ်းကြောင်းနှင့် စတင်ထုပ်ပိုးမှုတို့ကို ဆိုလိုသည်။အခိုင်မာဆုံးကုမ္ပဏီများသည် လုပ်ငန်းစဉ်ခေါင်းဆောင်များချည်းမဟုတ်တော့ဘဲ၊ ၎င်းတို့သည် စနစ်အဆင့် ပေါင်းစပ်ပါဝင်သူများဖြစ်သည်။

ဝိုင်ယာကြိုးများ ထိရောက်မှု၊ ပါဝါပေးပို့မှု၊ အပူပိုင်းဒီဇိုင်းနှင့် လှိုင်းသိပ်သည်းဆတို့သည် ယခုအခါ အမှန်တကယ် ထုတ်ကုန်စွမ်းဆောင်ရည်ကို ဆုံးဖြတ်ပေးပါသည်။

AI သည် အဆုံးစွန်သော မောင်းနှင်အားဖြစ်သည်။

AI နှင့် စွမ်းဆောင်ရည်မြင့်မားသော ကွန်ပြူတာများသည် မကြုံစဖူး လှိုင်းနှုန်း၊ စွမ်းအင်ထိရောက်မှုနှင့် သိပ်သည်းဆတို့ကို တောင်းဆိုသည်။သမားရိုးကျ အတိုင်းအတာဖြင့် ဤလိုအပ်ချက်များကို မဖြည့်ဆည်းနိုင်ပါ။လိုအပ်သည်-

- Ultra-high-bandwidth memory-compute အပြန်အလှန်ချိတ်ဆက်မှု

- လည်ပတ်မှုတိုင်းတွင် အလွန်အမင်း စွမ်းအင်ထိရောက်မှုရှိသည်။

- ကြီးမားသော ပြိုင်ဆိုင်မှုနှင့် သိပ်သည်းစွာ ပေါင်းစပ်မှု

AI သည် လုပ်ငန်းတစ်ခုလုံးအား သန့်စင်သော အတိုင်းအတာကို စွန့်လွှတ်ရန်နှင့် 3D ကွဲပြားသော ပေါင်းစပ်မှုကို လက်ခံရယူရန် တွန်းအားပေးခဲ့သည်။

နိဂုံး- အနာဂတ်သည် သေးငယ်သည်မဟုတ်ပါ၊ ပိုမြင့်သည်။

ထရန်စစ္စတာများ ကျုံ့သွားသည့် သက်တမ်းသည် မှိန်သွားသည် ။ဆီမီးကွန်ဒတ်တာများ၏ အနာဂတ်သည် စက်ပစ္စည်းများကို သေးငယ်အောင်ပြုလုပ်ရန်မဟုတ်ပေ—၎င်းသည် တည်ဆောက်မှုစနစ်များအကြောင်းဖြစ်သည်။ ပိုမိုမြင့်မားသော၊ ပိုသိပ်သည်းပြီး ပိုမိုထက်မြက်စွာ ချိတ်ဆက်ထားသည်။.

Planar မှ FinFET မှ GAA မှ CFET အထိ၊ ထရန်စစ္စတာသည် ၎င်း၏ ဆင့်ကဲဖြစ်စဉ်ကို ပြီးမြောက်ခဲ့သည်။နောက်တစ်ကြိမ် တိုက်ပွဲဝင်ရဦးမည်။ 3D ပေါင်းစပ်မှု၊ အဆင့်မြင့်ထုပ်ပိုးမှုနှင့် စနစ်အဆင့် ဒီဇိုင်း.ဤသည်မှာ လာမည့်ဆယ်စုနှစ်တွင် semiconductor ခေါင်းဆောင်မှု ဆုံးဖြတ်ရမည့်နေရာဖြစ်သည်။